http://www.avionicstech.com.cn

avionicstech@careri.com

DOI:10.12175/j.issn.1006-141X.2020.03.06

# 机载综合无线电平台的中频数据传输总线优选分析

武 龙. 沈 聪

(中国航空无线电电子研究所,上海 200241)

要]在综合无线电平台中,根据硬件平台通用化要求,需要选择一种总线同时满足 CNI 不同波形的中频 数据传输对延时、带宽和误码率的要求。本文针对不加协议的 GTX 和加上高速串行通信协议的 Aurora、SRIO 进行测试、得到这三种高速串行总线在延时、带宽和误码率的对比分析、从而选择一种总线作为多波形综合的 中频数据传输总线。

[关键词] 机载综合无线电平台; GTX; Aurora; SRIO; 中频数据传输总线

[中图分类号] TN859

[文献标识码]A

[文章编号] 1006-141X(2020)03-0028-06

# Optimization and Analysis of Intermediate Frequency Data Transmission Bus for Airborne Integrated Radio Platform

WU Long, SHEN Cong

(China National Aeronautical Radio Electronics Research Institute, Shanghai 200241, China)

Abstract: In the integrated radio platform, we are supposed to meet the requirements of hardware platform generalization. Then a bus is needed to meet requirements of delay, bandwidth and error rate of all kinds of CNI waveforms. Tests have been carried out in various protocols of high speed serial bus, including Aurora, SRIO and GTX without protocol. Comparative analysis of delay, bandwidth and error rate is obtained, and a proper high speed serial bus is chosen according to the requirements of the intermediate frequency data transmission in the Integrated Radio Platform.

Key words: integrated radio platform; GTX; Aurora; SRIO; intermediate frequency data transmission

综合无线电平台技术是采用模块化、标准化、 开放式的设计思想,对 CNI 等波形进行物理和逻辑 综合,从而构建系统架构开放、平台资源通用、波 形功能软件可配置的综合化系统。实现硬件平台通 用化提高系统可靠性、可扩展性、可维修性, 从而 降低系统体积、重量、功耗和成本。

分频段综合是综合无线电平台设计的基本策略,

收稿日期: 2020-05-22

理区是波形数据处理的基本思路。在CNI十几个波 形同时传输的系统链路中, 为了满足数字信号处理 资源通用化要求,波形数据传输链路通道需要同时满 足各类波形对传输数据带宽、误码率和延时的要求,

将相近频段的波形通过同一天线进行接收,将波形

数据初步处理后转换为中频数据,送到数字信号处

引用格式: 武龙, 沈聪, 机载综合无线电平台的中频数据传输总线优选分析 [J], 航空电子技术, 2020, 51(3): 28-33.

而中频数据传输则是将射频前端与波形信号处理区 连接的桥梁,是波形数据传输链路的核心,如何选 择一种高数据传输带宽、低误码率、低延时的中频 数据传输总线显得格外重要。

## 1 中频数据传输技术研究

根据不同波形资源需求分析,将功能相同、指标相近的资源功能进行分解和综合,可基本分为综合孔径分区、综合射频分区、信号处理分区和信息处理分区,同时物理层以上采用网络分区、IO接口分区和基本配置分区,组成功能完善、覆盖全面的相近波段的多波形综合化系统。由于各个波形的工作方式、接收灵敏度、发射功率、调制方式、通道带宽等相近,可以采用不同波形分时传输的思想,接收的模拟信号经限幅、预选、变频、放大、宽带滤波、A/D采样、预处理后,转换成中频数字信号处理模块进行处理。构建发射机时,将相应波形对应的数字信号经数字信号处理模块转换成中频调制信号,经变频、激励以及功率放大后由天线发射出去。

#### 1.1 波形数据传输要求

在多波形综合化系统中,内部数字信号处理资源、管理资源、射频信号处理资源和外围设备等需

要通过总线网络进行高带宽、低延时、低误码率的 大数据交互。通过分析综合化系统中常用到的波形, 整理各个波形运行时中频、数字通道所占用的带宽 量,可以得出系统运行时占用的带宽总量,现以 L 波段及个别专用波形等常被综合的波形需求为例, 选择需要使用的中频数据传输总线,波形需求如表 1 所示。

表 1 各类波形数据需求分析

| 序号 | 波形         | 业务数据        | 时延要求    |

|----|------------|-------------|---------|

| 1  | ADF/MB     | 10 k bit/s  | ≤100 μs |

| 2  | MLS/ILS    | 10 k bit/s  | ≤100 μs |

| 3  | TCAS       | 640 M bit/s | ≤100 μs |

| 4  | XFF        | 640 M bit/s | ≤100 μs |

| 5  | ATC        | 640 M bit/s | ≤2 μs   |

| 6  | TACAN/DMEP | 640 M bit/s | ≤100 μs |

系统内部传输数据主要分为业务数据和管理数据,其中 ATC 对时延要求很高,需要采用高实时、低抖动、高速率的数据传输总线,TCAS 等波形的数据速率在 640 Mb/s 以上,而且业务数据和管理数据在网络中传输具备可靠性的要求。

#### 1.2 常用总线性能对比

目前机载系统内部常用高速总线为 SRIO、 PCIE 和 LVDS 总线,对现有高速总线的软件开销、 网络、拓扑和时延进行对比分析,如表 2 所示。

表 2 高速总线性能对比

|    | , 122 MEIBAY        |            |              |                                      |                                        |                                      |

|----|---------------------|------------|--------------|--------------------------------------|----------------------------------------|--------------------------------------|

| 序号 | 对比项                 | PCIE       | SRIO         | LVDS                                 | GTX                                    | Aurora                               |

| 1  | 软件开销                | 高          | 中            | 无                                    | 低                                      | 较低                                   |

| 2  | 硬件纠错重<br>传          | 支持         | 支持           | 无                                    | 无                                      | 无                                    |

| 3  | 硬件开销                | FPGA       | FPGA         | FPGA+ 串并转换芯片                         | FPGA                                   | FPGA                                 |

| 4  | 传输速率                | 10 G bit/s | 6.25 G bit/s | 1.28 G bit/s                         | 6.25 G bit/s                           | 6.25 G bit/s                         |

| 5  | 传输模式                | DMA        | DMA/ 消息      | 无特定传输模式                              | 无特定传输模式                                | 无特定传输模式                              |

| 6  | 拓扑结构                | PCI 树      | 任意           | 点对点                                  | 点对点                                    | 点对点                                  |

| 7  | 直接点对点<br>对等互连       | 不支持        | 支持           | 支持                                   | 支持                                     | 支持                                   |

| 8  | 传输距离                | 中          | 中            | 中                                    | 中                                      | 中                                    |

| 9  | 数据包最大<br>有效载荷长<br>度 | 4096 字节    | 256 字节       | 不打包,无特定长度                            | 可选流模式及帧模<br>式,无特定长度                    | 可选流模式及帧模式,无<br>特定长度                  |

| 10 | 打包效率                | 82%        | 92% ~ 94%    | 不打包                                  | 根据包长度确定效率                              | 根据包长度确定效率                            |

| 11 | 延时                  | μs 级别      | μs 级别        | $16.5~\mathrm{ns}\sim44~\mathrm{ns}$ | $137.6~\mathrm{ns}\sim230~\mathrm{ns}$ | $153~\mathrm{ns}\sim256~\mathrm{ns}$ |

PCI-PCI 桥接设备只能用到树形体系结构中, 系统延时会增加,延时不稳定,且附带电路会增加, 从而增加系统的功耗、体积及成本。传统的综合化 软件无线电平台采用标准并行总线方式, 通过并行 连接方式将多种功能模块挂接在一起, LVDS 总线 是最常用的一种并行总线。但受限于 LVDS 总线传 输速率低,且在板间传输过程中,发送模块和接收 模块需要采用同源时钟,不仅如此,LVDS 总线在 传输过程中需要在发送模块和接收模块硬件电路中 设计串并转换芯片、串并转换芯片面积较大、功耗 较高, 使得传输 LVDS 总线路数受限, 串并转换芯 片占用模块内部印刷电路板 (PCB: Printed Circuit Board) 空间,增加系统功耗,而高速串行总线可以 采用恢复时钟的方式保证收发模块采用同一时钟, 而不需要单独设计时钟模块为发送模块和接收模块 提供时钟,且高速串行总线可以直接从FPGA引出, 不需要附加电路,从而减轻系统硬件开销、设计复 杂度和维护难度,因而考虑采用技术指标满足要求 的高速串行总线技术代替传统的并行总线技术传输 中频信号。

# 2 不同协议的高速串行总线分析

本文针对其中较为常用的不带特定协议的GTX、带Aurora协议的GTX和SRIO这三种协议的总线进行测试及对比分析。首先搭建了基于Kintex-7FPGA的硬件测试平台;然后设计并分别实现三种协议的高速数据通信;最后结合测试结果,从协议层次结构、传输延时、实际带宽和误码率三个方面进行了比较。在多波形综合的产品中,可为中频数据传输总线协议的选用、测试和工程实现提供参考。

#### 2.1 高速串行总线技术

高速串行总线技术是新一代高速数据互联技术的发展方向,以串行 I/O 取代源同步并行 I/O,以差分方式取代单端方式,以 Point-to-Point(点到点)方式替代 Big Pipe(基础动态网页服务体系)方式,以交叉开关结构取代共享总线,高速串行总线优势如下。

- (1) 差分信号传输方式比单端传输方式对共模输入噪声有更强的抵抗能力。

- (2) 点对点互联方式,对链路来说负载固定且

小,时钟频率可进一步提高。

(3) 交叉开关结构利用新一代开关器件结合分组交换技术实现交叉开关网络。系统中多个点到点的通信链路被组织起来,实现系统内所有芯片或模块见的任意互传和并发传输,系统带宽成倍增加。

吉比特收发器在这样的环境下应运而生。 XINLINX公司在已有的 RocketIO 的基础上开发出了可以传输更高速率的 GTX 收发器。业界广泛使用的 Xilinx 公司 Kintex-7 系列 FPGA 支持多种高速串行通信协议,Kintex7 系列的 GTX,以其良好的 DFE 性能、功耗表现及 DFE 性能,能提供高达12.5Gbps 的过背板能力,且能支持在插入损耗高达30dB 的信道上可靠传输,从而得到广泛应用。。

在众多 SERDES 应用中,本文涉及到常用高速总线有 PCI-e、SRIO、不带协议的 GTX 和 Aurora 四种,鉴于 PCI-e 总线采用树状结构,传输延时高,无法有效支持点到点传输,软件开销较大和传输效率较低,而在综合化系统中,中频数据需要点到点传输,且对延时和传输效率有很高的要求,故不采纳 PCI-e作为中频数据传输总线,本文着重对不带协议的GTX、Aurora 协议的 GTX 及 SRIO 这三种高速串行总线进行分析。

# 2.2 GTX 高速串行总线技术介绍

GTX 收发器的数据输入、输出通道采用一对差分线,器件引脚数较少、降低了对 PCB 空间要求、PCB 层数较少、可以轻松实现 PCB 设计、连接器较小、电磁干扰降低并具有较好的抗噪能力,为超大带宽数据传输提供了可行性。Kintex-7 FPGA GTX 收发器比 VIRTEX-6 FPGA GTX 收发器性能更高,功耗表现更好,使用更简便。在 FPGA 与 FPGA 间只需两对差分 I/O 资源和少量的控制信号线即可进行数据传输交互,并且抗干扰能力较强,使数据的传输的误比特率更小,GTX 收发器原理框图如图 1 所示。

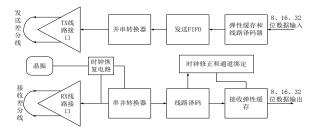

图 1 GTX 收发器发送和接收结构框图

在发送端,来自 FPGA 内部的 8 或 16 或 32 位的并行数据先通过弹性缓存后进行线路编码(也可不选),然后进入 FIFO 后发给并串转换器(PISO: Parallel In Serial Out),转换成差分串行信号后由 TX 线路接口发送出去。接收端先进行时钟数据恢复电路、线路译码(也可不选,但要与编码对应),恢复出时钟和数据后便可进入 RX FIFO 进行时钟校验(Clock Correction)和通道绑定(Channel Bonding),最后发送给 FPGA 内部进行相应的处理。

采用 Xilinx 公司的核生成器可以很方便生成GTX 模块,配置用户所需要的参数后可生成相应的GTX IP 核。

## 2.3 基于 Aurora 协议的高速串行总线介绍

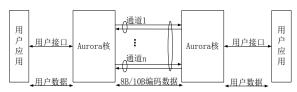

Aurora协议就是 Xilinx 公司在 GTX 总线上的基础上,提供的一个开放、免费的链路层协议。 VIVADO 套件中关于采用 8B/10B 编码的 Aurora 的 IP 核是在 Aurora 协议和高速串行收发器 Rocket 基础上研发出来的硬核。Aurora 核嵌入在 RocketIO 模块中,提供简单的用户接口,极大方便了信号的可操作性。通过 IP 核的用户界面可改变 RocketIO 中复杂的控制结构,AuroraIP 主要包括本地流控制、用户流控制、用户数据接口、时钟输入与时钟修正模块,高速串行收发模块和状态信息控制模块。 Aurora 协议是一款可自由使用相对简便的点对点协议。AuroraIP 支持与光纤的无缝连接,传输过程中,抗电磁干扰能力强,集成度高,具有很强的灵活性。基于 Aurora 8B/10B 协议的 Aurora 链路结构示意图如图 2 所示。

图 2 Aurora 链路结构示意图

### 2.4 SRIO 高速串行总线技术介绍

SRIO 总线是一种分组交换结构总线,采用包交换技术,在网络处理器(NPU补充全称)、中央处理器(CPU)和数字信号处理器(DSP)之间的通信具有高速、低延迟、稳定可靠的互联性,SRIO接口采用 XILINX VIVADO 套件中提供的 Serial RapidIO 2.0 的 IP 核实现。可提供 6.125 G bit/s(1.25Gb/s,4x)的带宽(Rev2.0 规范可提供 40 G bit/s 带宽),

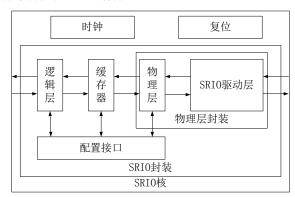

其所有的协议都是由硬件实现的,软件开销较小。 SRIO 精简了端点定义,可以装在 FPGA 中,只占芯片面积的很小部分。SRIO 主要特性是具有极低的延迟性(交换设备端到端延迟典型值约 200 ns)和高带宽,比 PCI、PCIE 延迟都低的多;并且具有高可靠性,基于硬件的错误恢复和重传和链路层每80个字节插入 CRC。适用于芯片与芯片、板与板、系统与系统之间的高速数据传输。采用 CPS1848 等SRIO 专用交换芯片,可实现多节点、不同类型芯片数据的高效互联互通。Xilinx 公司的 Kintex-7 FPGA 芯片内部的 SRIO 架构框图如图 3 所示。

RapidIO协议分为逻辑层、传输层和物理层 3 层结构。逻辑层定义了包格式和操作、事务、事务 排序等概念,支持 I/O、消息传递和全局共享寄存器 等编程模型。传输层为数据包提供路由和寻址功能。 物理层定义了链路包交换协议、流量控制和差错控 制等功能以及电气特性。

图 3 SRIO 系统框图

远端读取本地数据时发来 NREAD,本地 TREQ 收到此命令负责接受此请求,然后读出数据,从TRESP 将数据发回给远端; TREQ 是接收远端发来的请求,TRESP 是给远端发的回应。Doorbell 和message 直接和端点联系,Doorbell 最多 16 个字节,message 最大支持 4096 个字节。用 SWRITE 存储大批量的数据,包头比较少,但发送的字节数是 8 字节的倍数;如果接收端给应答则需要 NWRITE\_R 额外的包头开销。

## 2.5 高速串行总线测试平台

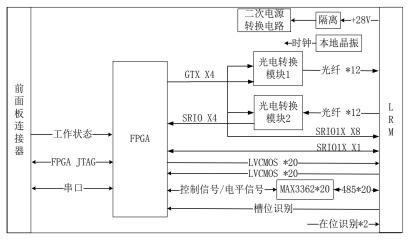

在机载无线电综合化设备中,采用的中频接口测试硬件平台符合 ASAAC 标准,该硬件平台可实现光信号与电信号的转换,并通过连接器的 MT 接头将光信号传输出去,如图 4 所示。

图 4 中频接口测试硬件平台框图

在平台搭建过程中,采用 FPGA 的型号为 XC7K410T-2FFG900I,该芯片含 20 个以上 GTX 收 发器,链路线速率可达 6.6 Gb/s,支持 1x、2x 和 4x 链路。光电单元主要由收发光模块构成,接收光模块的型号为 HTA8529-MH+001SA 和发送光模块型号为 HTA8528-MH+001SA,它包含 4 条链路,带宽可达 40 Gb/s。模块之间采用接口与 LRM 连接器光接口匹配的光纤进行连接,通过光信号进行高速数据交换,同时可以在测试夹具上通过电信号形式进行高速数据交换。

#### 2.6三种高速串行总线性能对比

本节通过延时、误码、传输带宽三个角度分析不带协议的 GTX、带 Aurora 协议的 GTX 和 SRIO 这三种协议之间的性能差别。为了保证测试结果的准确性,测试设备采用同一套 LRM 模块及测试线缆。三种协议的总线参数配置尽量相同,即同时配置为双工模式、参考时钟相同、采用 8B/10B 编码模式。

#### 2.6.1 GTX、Aurora 及 SRIO 协议的延时分析

在进行数据传输延时测试中,采用单模块自发自收的模式,光纤采用固定长度 2 米。设置特定数据包头和数据长度分别为 4K、128K、4M 的帧长度的数据,发送时进行计数,经过外部光纤自环,本模块接收到数据后,停止计数,根据当前的时钟频率和计数获得经过该协议传输延时。传输速率为 6.25 G bit/s,三种协议的传输延时如表 3 所示。

表 3 三种协议在 6. 25Gbps 速率下的延时测试结果

| 延时   | GTX      | Aurora   | SRIO    |

|------|----------|----------|---------|

| 4K   | 137.6 ns | 153.6 ns | 1.73 μs |

| 128K | 137.6 ns | 153.6 ns | 1.72 μs |

| 4M   | 137.6 ns | 153.6 ns | 1.73 μs |

通过三种协议的在不同速率下的延时分析,可以得到 GTX 和带 Aurora 协议的高速串行总线的传输延时在 300 ns 以下,能满足综合化系统中常用波形对中频数据传输的低延时要求。而 SRIO 总线的延时在 1 μs 以上,且考虑到在综合化系统中的链路延时,不能满足对延时要求苛刻的 ATC 波形的要求。

#### 2.6.2 GTX、Aurora 协议及 SRIO 协议带宽分析

在进行三种高速串行总线传输带宽测试中,分别采用包长度为 4 kbit、128 kbit 和 4 Mbit 带有固定包头的数据。采用两块相同的 LRM 模块,并通过接口匹配的光纤将两个 LRM 的光纤接口进行连接,光纤长度固定为 2 米。一个 LRM 模块用于发送数据,另一个 LRM 模块用于接收数据,在两个 LRM 模块内设置相同长度的时间窗,LRM 模块在有效时间窗内分别使用这三种协议持续发送长度分别为 4 K bit、128 K bit 和 4 M bit 的数据。

在三种不同协议下的带宽测试过程中,在接收 LRM 模块内部第一个接收到数据后,开始进行拉升时间窗的上升沿,经过与发送端相同时间窗后接收到的有效包数量。通过对比发送端的数据量和接收端的数据量,可获得在三种不同高速串行协议在6.25 G bit/s 速率下的数据传输带宽,如表 4 所示。

表 4 GTX 协议在 6. 25Gbps 带宽测试结果

| 带宽   | RX         | TX         | 带宽效率   |

|------|------------|------------|--------|

| 4K   | 1738958576 | 1745751419 | 99.61% |

| 128K | 365316379  | 365361014  | 99.99% |

| 4M   | 425593386  | 425595045  | 100%   |

在 Aurora 协议及 SRIO 协议的测试过程中,直接根据相同时间内的接收数据和发送数据计算出实际传输带宽,测试结果如表 5 所示。

表 5 Aurora 和 SRIO 协议在 6. 25Gbps 带宽测试结果

| 协议     | 带宽   | 传输实际带宽    | 带宽效率   |

|--------|------|-----------|--------|

| Aurora | 4K   | 310.78 MB | 99.45% |

|        | 128K | 311.96 MB | 99.83% |

|        | 4M   | 311.99 MB | 99.83% |

| SRIO   | 4K   | 270.27 MB | 86.49% |

|        | 128K | 270.27 MB | 86.49% |

|        | 4M   | 270.27 MB | 86.49% |

通过对三种协议的高速串行总线在不同包长和实际带宽的测试,可以获得不带协议的 GTX 与带 Aurora 协议的高速串行总线的实际传输带宽效率在 99% 以上,而 SRIO 的实际传输效率在 86.5% 左右,远远小于前两种的传输带宽效率。

## 2. 6. 3 GTX、Aurora 协议及 SRIO 协议误码率分析

通过 IBERT 工具进行了三种协议误码率测试。 IBERT 是 Xilinx 提供用于调试 FPGA 芯片内高速串 行接口比特误码率性能的工具,具备实时调整高速 串行接口的多种参数、与系统其他模块通信及测量 多通道误比特率等功能。可以动态调整发送数据的 时间来动态调试测试数据量。根据实际测试结果, GTX、Aurora 协议及 SRIO 协议的高速串行总线的 误码率都为 0,三种总线均满足中频数据对传输误 码的要求。

#### 3 结束语

机载综合无线电平台中频数据传输总线的选择 需要对延时、数据速率和可靠性进行权衡。根据对 GTX、Aurora 协议及 SRIO 协议三种高速串行总线 的延时、带宽、误码性能的分析,无协议的 GTX 延 时最小,可靠性最低,有硬件纠错重传机制的 SRIO 协议可靠性最高,延时最大,而 Aurora 协议在延时和可靠性方面性能居中。

根据测试得到 SRIO 协议延时在 lus 以上,传输带宽效率达不到 90%,已经无法满足部分波形对延时和带宽的要求,而 GTX、Aurora 协议延时在 200ns 左右,带宽传输效率在 99% 以上,能够满足在机载综合化系统中常用波形中频数据传输对总线的性能要求。不带协议的 GTX 总线无法对接收数据进行实时控制,无法满足机载综合无线电平台中频数据传输对高可靠性的要求,Aurora 协议在延时、带宽传输效率方面,与不带协议的 GTX 性能差别不大,但是 Aurora 协议对数据传输的可靠性提供了极大的保障,故在机载综合无线电系统中,可以优先选择 Aurora 协议作为多波形信号的中频数据传输总线。

### 参考文献

[1] 张德民. TD\_LTE 中基于 GTX 的数据交互的设计 [J]. 重庆: 重庆邮电大学. 2013.

- [2] 李坤,朱红. Virtex-6 GTX 高速串行传输原理与仿真 [J]. 四川,成都:电子科技大学. 2010.

- [3] 吕鹏 . 基于 SRIO 总线的全交换路由设计与实现 [J]. 无线电通信技术, 2017, 43(2):87-89, 98.

- [4] E. KOSKI, C. L. LINN. The JTRS program: software defined radios as a software product line[A]. 10<sup>th</sup>th International Software Product Line Conference [C]. RF Communications Division. Harris Corp. Palm Bay, FL, USA.