avionicstech@avic.com

DOI:10.12175/j.issn.1006-141X.2022.03.08

## 基于 TMS320F28335 的一种多机多通道通讯方法的设计

杨 舟,蔡冬生

(中国航空无线电电子研究所,上海 200233)

[摘 要]TMS320F28335 是TI公司的一款数字信号处理芯片,具备丰富的外设接口,器件可靠性强,在机载机电、接口、控制领域得到应用。面对嵌入式控制器多机通讯的需求,使用TMS320F28335 的 McBSP 接口和DMA 功能设计一种时分复用的多机多通道通讯方法,硬件接口直连,软件通过DMA 自动完成帧数据收发,避免通讯对DSP 内核的占用,实现一种经济、可靠的多机通讯方案。

[关键词]TMS320F28335; McBSP; DMA; GPIO

[中图分类号]TN911.72

[文献标识码]A

[文章编号]1006-141X(2022)03-0053-06

# A Multi-Channel Parallel Communication Design for Multi-Embedded Controllers Based On TMS320F28335

#### YANG Zhou, CAI Dong-sheng

(China National Aeronautical Radio Electronics Research Institute, Shanghai 200233, China)

**Abstract:** TMS320F28335 is a digital signal processing chip from TI company, which has rich external interfaces with high reliability.TMS320F28335 is applied widely in the field of airbone electrical, interface and control. A method with McBSP interface and DMA function is designed for the demand of the multi-machine communication by embedded controllers based on TMS320F28335. The hardware interfaces of multi-controllers are directly connected, and the software automatically completes the data transfer through the DMA by this design, avoiding the occupation of the DSP kernel by the communication. This design realizes an economical and reliable multi-machine communication solution.

Key words: TMS320F28335; McBSP; DMA; GPIO

TMS320F28335 是由美国德州仪器公司(TI)研制开发的数字信号处理器(DSP: Digital Signal Processing),具备运算专用 DSP 指令集和超长指令字架构,具有丰富的外设接口,曾在具有运算需求或大数据量浮点数据处理的机载、舰载装备信号处理、新能源和工业控制领域得到广泛应用。随着技术发展,芯片集成度广泛提升、主频提高,

TMS320F28335 的浮点运算能力在信号处理芯片领域已不属于领先水平,但因其工艺稳定、器件可靠性强,在长期高安全等级应用中积累的大量稳定应用案例,使其在机电、接口、控制等装备需求领域仍存在广泛需求。

TMS320F28335 具有丰富的外设接口<sup>[1]</sup>,包括传统的异步收发传输(UART: Universal Asynchro-

收稿日期: 2021-08-09

nous Receiver/Transmitter)、串行外设接口(SPI: Serial Peripheral Interface)、控制器局域网(CAN: Controller Area Network)等通用串行接口、外部存储器接口(EMIF: External Memory Interface)/LocalBus(CPU本地总线)并行接口,除常见通用接口外,该芯片具有 TI 独有的多通道缓冲串行接口(McBSP: Multi-channel buffered serial port),可以根据时分复用的机制完成多机多通道通讯 [2]。同时,芯片内具有直接内存访问(DMA: Direct Memory Access)功能模块 [2],支持外设接口和内部存储空间直接进行数据交换,不需 DSP 进行主动干预,可以和其他外设接口组合实现大规模数据的自动收发。

在机载机电、接口、控制领域,多个嵌入式控 制器之间通讯信息的高效、可靠传输是高可靠性系 统设计的重难点, 重要的控制信号一般使用离散量 控制,小规模的控制信号可采用点对点的串行通讯 接口(UART/SPI等),大规模的数据传输一般使用 点到点的并行通讯接口(EMIF 或 LocalBus)或高速 差分总线接口(PCIE/RapidIO/Ethernet),并适配机 载通讯网络协议。对于非大规模(包含控制/反馈/ 采样指令,具有高安全性、高实时性要求)多空置 器之间的通讯信息的传输,功能性能匹配、并具备 经济性的传输方式并不易选择: 离散量接口数量有 限,难以满足通讯信息的规模;点对点的串行/并 行接口数量有限,一般单控制器芯片同一种通用串 行接口不多于2个,并行接口一般只有1套,一发 多收/多发一收等常见主从控制方式的通讯接口互 联设计困难; 支持桥接、交换机等方式的高速差分 通讯方式(PCIE/RapidIO/Ethernet)实现的软硬件开 销偏大,尚未在机载机电、接口、控制领域得到推广。

在一主多从的嵌入式控制器通讯应用场景中,多从机可复用主机的同一套串行总线(UART/SPI),但一般需要主机提供多个通用离散量控制接口(GPIO: General-Purpose Input/Output)作为串行通讯从设备的选通信号,若从设备通过离散量逻辑判断是否和主机进行有效通讯,则n个离散接口可以选通2<sup>n</sup>个从设备;若从设备直接将离散量接口转至串行总线选通端(如SPI接口的CS端),则主设备在对n各不同的从设备进行通讯时除了串行总线外需要增加n个离散量接口信号,占用硬件资源较大。在机载应用领域,一主多从的设计模式中,

主设备一般会选用主频较高,处理能力较强的处理器(精简指令集中央处理器 PowerPC: Performance Optimization With Enhanced RISC – Performance Computing,高性能 DSP等),用于高实时性的应用部署,此类处理器外设低速接口(如 GPIO)不会太多,过多的从机通讯选通信号会带来设计的困难。

此外,主从设备进行串行总线通讯,每一次通讯一般包括建立链接、握手、数据通讯的过程,在机电、接口、控制等机载高可靠性应用领域,每一帧通讯后还需要校验过程,在一主多从模式下,采样离散量信号选通的串行通讯方式对多个从设备进行轮询,则实际数据通讯意外的握手、校验等开销相对较大,对于以毫秒为周期的定时应用不可忽视。

在机载机电、接口、控制应用领域一对多主从设备通讯模式中,在从设备较多的情况下,希望仅使用1套串行总线接口本身能完成单主设备对多个从设备的分别通讯,节省离散量资源,节省通讯时间开销。

本文利用 TMS320F28335 提供的 McBSP 接口和 DMA 技术,实现一种多控制器多通道通讯方法,利用 McBSP 时分复用的技术,一主多从多控制器同一组接口直联,同步串行收发,实现机载机电、接口、控制领域经济可靠的多机通讯。

#### 1 McBSP 多通道通讯机制

#### 1.1 多机连接方式和接口定义

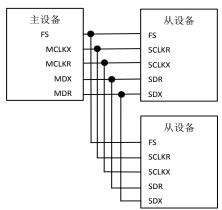

McBSP 是 TI 提供的 5 线制同步串行接口,在 TMS320F28x、TMS320C665x、TMS320C67x 等 系 列 DSP 中部署。在使用 McBSP 多通道模式实现一 主多从通讯方式时,5 线制接口的物理连接方式如下:

FS: 帧同步信号,每一帧数据为单次所有时分复用多通道数据包的组合,所有主从设备共1个FS,主设备配置为输出,即帧同步信号产生方,从设备配置为输入,即接收方;

MCLKX-SCLKR: 主发从收时钟, 所有从设备 共用1路, 主设备配置为输出, 从设备配置为输入;

MCLKR-SCLKX: 主收从发时钟,所有从设备 共用1路,主设备配置为输出,从设备配置为输入;

MDX-SDR: 主发从收串行数据线,所有从设备 共用1路; MDR-SDX: 主收从发串行数据线,所有从设备 共用1路。

其中 MCLKX-SCLKR 和 MCLKR-SCLKX 使用 主设备内部同一个时钟源,即所有数据通讯时钟由 主设备产生。

图 1 McBSP 一主多从物理连接方式

如图 1 所示,多从机连接在单主机的同一套 McBSP 接口上,在物理上"并行"连接,主机并 不需要为每个从机增加片选离散量信号,每一个 McBSP 帧发送的过程中,帧信息会并行发送到每一 个从机,不同的从机则遵循 McBSP 的多通道通信机 制对并行收到的数据帧进行解帧和按序回发。

#### 1.2 多通道通信机制和配置

McBSP 多机通讯使用时分复用的方式,每一帧(Frame)数据含多包数据,每包数据对应每个通道(Channel),同一帧中不同包数据按设计分配给不同从机。主机发送端口将该帧数据通过直连的McBSP 接口向所有从机同步发送,从机各自配置该帧数据中的哪一包或哪几包数据由本机接收,从机各自从收到帧同步信号开始按接收时钟(MCLKR)进行计数,计数到本机有效数据包的对应的接收时钟时使能本机接收通道,实现对该帧数据中对应的数据包的接收,非本机配置的有效数据包对应的其他帧数据通信时间内,通道关闭,不接收发送给其他从机的数据。

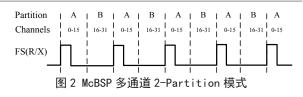

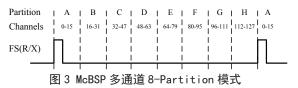

McBSP 多机通讯包含 2-Partition(2 分区)和 8-Partition(8 分区)两种模式,可分别对应配置为 单帧 32 包数据和单帧 128 包数据的传输模式,时序 如图 2 和图 3 所示。

图 2 和图 3 中, Partition 对应 McBSP 通讯区间, 每区间包括 16 个 Channel, 2-Partition 模式下,每一 帧数据包含 A 和 B 两个 Partition,即一共包含 32 个 Channel 的数据; 8-Partition 模式下,每一帧包含 A-H 8 个 Partition,即 128 个 Channel 的数据;

Channel:数据通道,即数据包,每个 Channel 包含1个 Word 数据,Word 可配置为最大 32-bit, 主机和从机可分别配置 Channel 使能通道。

FS: 帧同步信号,每个帧同步信号在帧头出现一次。在多通道通讯模式设计过程中,设计师规划好主机端发送的每一帧的 32 包或 128 包数据如何分配给不同的从机,各从机使能对应的 Channel 号,各从机从接收到帧同步信号后开始计数,在对应数据包(Channel)处接收属于本从机的数据,实现多机同步收到的数据帧时分复用拆解,各从机仅获取分配给自己的数据。

各从机向主机发送数据使用收发同步的方式,即各从机接收帧的同时按使能的发送 Channel 和时钟计数向数据线发送本机使能的 Channel 对应的数据,各从机不同时间在同一根数据线上发送不同Channel,直至填满该帧数据。

需要注意的是,设计师在分配主机向从机发送的数据帧时可以将某些 Channel 配置为一发多收的广播或组播模式,但在分配从机向主机发送组帧的 Channel 时,各从机的 Channel 务必独立,避免数据串扰和电气故障。

#### 2 McBSP+DMA 数据自动收发方法设计

根据 McBSP 接口设计, McBSP 的发送和接收可以采用轮询状态寄存器、中断或 DMA 触发方式进行。发送/接收状态寄存器中可供 DSP 查询的状态为 DXR/DRR(数据发送寄存器/数据接收寄存器)

满/空状态,即单个Word/Channel的数据收发状态, 无法查询单帧多数据收发过程的整体进度、状态。 McBSP 提供的中断事件也仅包括 DXR/DRR 满/空 中断,即单个Word/Channel 数据收发完成中断,无 法为帧数据整体收发完成设置单独的中断。因此若 使用轮询和中断方式进行多通道模式收发,需要对 帧内每一个通道的数据进行轮询/中断并计数判断 整个帧的发收进度,会占用大量的 DSP 运行资源, 不具备实用性。

使用 TMS320F28335 的 DMA 功能,可配置一个 DMA 通道源地址为通讯数据源存储空间,目的地址为 McBSP 的数据发送寄存器,另一个 DMA 通道源地址为 McBSP 数据接收寄存器,目的地址为通讯数据目的存储空间,DMA 通道事件数对应 McBSP 帧内有效 Channel 数据数。使能发/收 DMA 通道后,DMA 模块可在无 DSP 主动干预的情况下,将 McBSP 单个 Word/Channel 的数据顺次收/发至相应存储空间,在达到整个帧数据对应的计数值后,产生单独的 DMA 收/发完成事件,DSP 可通过对 DMA 状态寄存器轮询或 DMA 事件中断的响应判断 McBSP 帧数据整体收/发的完成,即使用 DMA 功能模块,将 McBSP 的帧事件整体转换为 DMA 的单独事件,不再占用 DSP 内核处理每一个 McBSP 通道的数据收发。

主机使用 McBSP+DMA 方式进行数据收发,分别配置 DMA 发、收通道并使能后,主机主动发起 McBSP 帧传输事件,考虑到 McBSP 收发同步的通讯方式,可对 DMA 发、收任意事件状态寄存器进行状态轮询或响应发、收完成任意中断,即可完成主机对从机的单帧多通道收发过程。

对于从机而言,应在主机使能发送之前配置完成 DMA 发、收通道并使能,等待主机的帧同步和时钟信号,采用轮询 DMA 任意发、收事件状态寄存器或响应中断的方式判断主机发起的通讯是否完成,从机宜使用中断方式对通讯进行响应<sup>[2]</sup>,避免主机不发起通讯的情况下轮询模式对 DSP 主核的占用。

#### 3 通讯同步机制设计和通讯配置流程

使用 McBSP+DMA 方式实现主从多机通讯,在

任意控制器状态异常并恢复正常状态的情况出现时,如果不采用额外的主从同步方法,会导致通讯不同步的问题。

根据 TMS320F28335 提供的 DMA 模块功能, DMA 仅能对 McBSP 每一个收/发事件的到来进行 监控和计数,计数到达配置值后触发 DMA 整体事件, 不会对 McBSP 帧同步信号进行判断,也不能对任一 个 McBSP 的事件进行超时 / 异常判断。在正常通讯 模式下, DMA 事件的计数起点和 McBSP 帧起点开 始的第一个事件必须严格对应, 否则主从机对各自 使能的通道判定会出现错误。若通讯开始后,任意 主从机出现异常情况断线,并通过某种方式恢复功 能后,配置和重新使能的 DMA 事件计数将从 0 开始, 此时其他正常的主从机若正好发/收至某帧中间部 分, DMA 事件计数非 0, 则异常恢复的控制器节点 和正常运行的控制器节点将出现 McBSP 通道失配, 收发数据无法按照设计的方式在多机进行正确分配, 整个多机通讯系统将处于混乱状态, 因此必须引入 其他方式在多机收发开始之前进行同步。

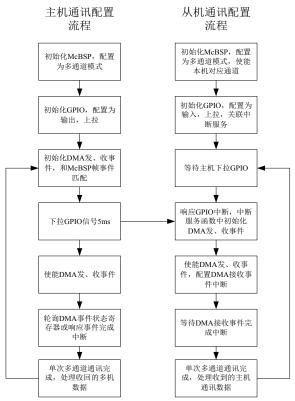

本文设计在主机和从机之间增加一根 GPIO 控制信号线,主机配置该 GPIO 为发送、上拉模式,从机配置配置为接收、上拉模式。从机上电后配置该 GPIO 下拉中断事件,等待上位机发起同步;上位机在进行每次 McBSP 的多通道帧传输之前,下拉GPIO信号,等待 50 μs后开始 McBSP+DMA 帧传输;所有下位机以该 GPIO 中断信号作为新一次 McBSP通讯的起始信号,在该 GPIO 信号的下拉事件中断服务函数中执行以下操作:

- (1) 从机 DMA 寄存器清除 DMA\_McBSP 发送通道所有事件;

- (2) 从机 DMA 寄存器清除 DMA\_McBSP 接收通道所有事件;

- (3) 从机 DMA 寄存器重置 McBSP 接收和发送通道;

- (4) 从机使能DMA\_McBSP发送通道和DMA McBSP接收通道。

依靠增加的 GPIO 同步控制信号设计,确保主机在开始任意一次 McBSP 多通道帧传输之前,所有从机已配置为等待 McBSP 帧头到来的状态,每一个McBSP 帧收发流程独立,避免通讯偶发异常状态造成通讯持续失序。

在实际机载机电、接口控制等应用中,主从机一般需要对每一个收到的 McBSP 通讯帧做校验,主机保存并处理符合校验信息的帧,丢弃错误帧并重发;从机保存并处理符合校验信息的帧,丢弃错误帧并在下一次回发中反馈通讯状态,McBSP 通讯的重传机制由应用实现,而依靠 GPIO 中断实现的单帧初始化机制保证了每一帧的独立性,避免了偶发性通讯帧错误的累积。

根据本设计,实现 TMS320F28335 一主多从多机多通道通讯需要正确配置,联合使用芯片的GPIO、McBSP 和 DMA 三种控制器,并结合中断服务或轮询的方式实现主从通讯, TMS320F28335 主机和从机实现多机多通道通讯配置流程如图4所示。

图 4 TMS320F28335 多机多通道通讯主从机配置流程

#### 4 多通道通讯方式的应用和优势

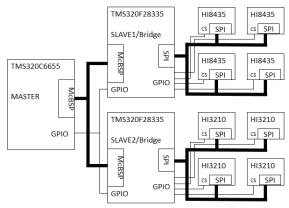

在机载某型号远程数据接口单元(RDIU: Remote Data Interface Unit)演示认证项目中,对本文提供的主从多机多通道通讯方式进行了应用,如图5 所示。

上位机为 TMS320C6655,具备 McBSP 接口。 下位机为两个 TMS320F28335,下位机 1 通过 SPI 接口完成对 4 个 HI8435 芯片进行离散量信号采集, 4个 HI8435 芯片的选通通过 4路 GPIO 信号完成; 下位机 2 通过 SPI 接口完成对 4个 HI3210 芯片进行 ARINC 429 协议串行通讯, 4个 HI3210 芯片的选通 通过 4路 GPIO 信号完成。下位机 1 和下位机 2 作 为中间设备(桥设备),实现对 HI8435 和 HI3210 外设群的控制,实现外设信息和上位机之间的交互。 按照应用需求,上位机和下位机之间需要按固定频 率(5 ms 周期)频繁通讯,上位机分别对下位机 1 实现离散量信息交互,对下位机 2 实现 ARINC 429 通讯收发。

图 5 某型 RDIU 多机多通道通讯方案

上位机和两个下位机之间通过 McBSP 接口进行通讯,通过一个共用的 GPIO 接口进行通讯同步。每个固定通讯周期 McBSP 配置为 128 个 16 位通道,每个下位机占用 64 通道,上位机在发送之前按照应用需求对两个下位机的通讯信息分别组帧,并合成一个整体 McBSP 通讯帧,并和上位机的 DMA 通道连接,在通讯开始时,使能 DMA 通道,发起对下位机的通讯。按照 McBSP 1Mb 通讯速率,每一个周期内的通讯需要耗时 2 ms,占整个通讯周期的40%。利用 DMA 通讯不占用 CPU 的特性,在通讯发起后 CPU 资源得到解放,不需在 2 ms 通讯期间等待或查询通讯状态,只需在通讯结束后响应 DMA完成中断。即上位机和下位机均可以在 5 ms 通讯周期内持续对其它应用线程、功能进行响应,大大提高了处理器的利用率。

综上所述,项目使用 McBSP+DMA 的多机多通 道通讯方式,串行接口物理并联,节省了用于片选 从机外设的离散量引脚,同时应用 DMA 技术,大 大减少了串行通讯过程对 CPU 的占用率。

### 5 结束语

本文通过对 TMS320F28335 提供的 McBSP 接口和 DMA 功能模块的联合应用,并结合 GPIO 同步信号的控制,设计了一主多从多机多通道通讯方法。多机通过同一组 McBSP 接口直连,通过时分复用的通讯机制实现多通道通讯,硬件设计简单,为机载机电、接口、控制领域的多机通讯需求提供一种经济、可靠的解决方案。

#### 参考文献

[1]Texas Instruments. TMS320F28335,TMS320F28334,TM S320F28332 Digital signal controllers data manual[EB/OL]. ZHCS889P datasheet,June. 2007. https://www.ti.com.cn/cn/lit/gpn/TMS320F28335.

[2]Texas Instruments. TMS320x2833x, TMS320x2823x technical reference manua[EB/OL]. SPRUI07 datasheet, Mar. 2020. https://www.ti.com.cn/cn/lit/pdf/sprui07.